Hi,

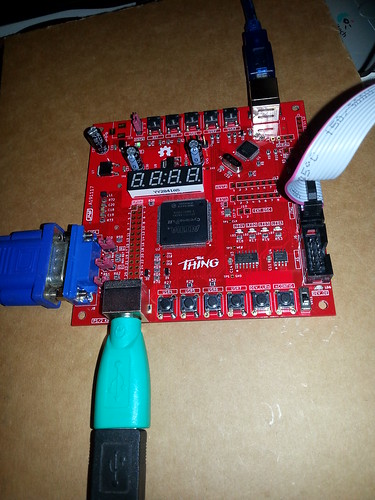

I've designed an "homemade" FPGA dev board (EP2C5T144C8N based) and I'm currently making the first tests.

I've used one of the "dual-purpose" FPGA pins to drive a LED too (see LED4 on the attachment jpg). The FPGA pin is ASDO.

The board uses an EPCS4 as eeprom in AS mode.

In the Cyclone datasheet (ehm... they call it "handbook"...) they says that the "dual-purpose" pins can be used as normal I/O after configuration if JTAG is used (not if AS is used).

More, there is a bug in Quartus II v13sp1 (the last one version that supports Cyclone II) on the "dual-purpose" pins and you have to chose "Passive Serial" mode when compiling to avoid an error (when using JTAG to transfer the bitstream to the FPGA the AS or PS mode selection is irrelevant...).

I'm able to compile and transfer the bitstream successfully (and without any error in the compile phase) to the FPGA using JTAG, but the Led on the ASDO pin doesn't turn on.

More, in the Quartus II fitter output the ASDO line seems correctly set as an user I/O output pin...

I'm sure that the Led works because in the AS mode, when the FPGA loads the bitstream from the EPCS4 eeprom, that Led is active showing the load phase.

Anyone has experimented anything about this (I haven't found any indication on the Altera/Intel forum or docs about this, and I know that is very "specific", but I'm curious...)?

BTW: In the second attachment there is the part of the Cylone II Hanbook (

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyc2/cyc2_cii5v1.pdf Table 1311) that says that it is possible...

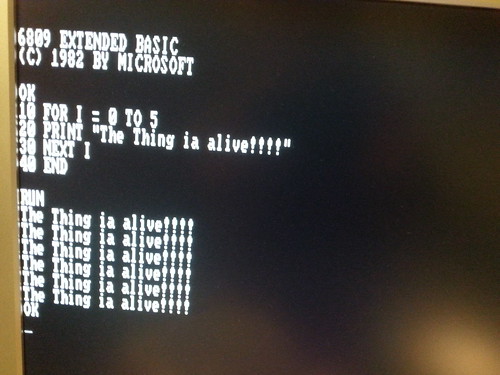

BTW2: Of course I'll publish here all the details when fully tested... Up to now it seems to work.. here "running" a SOC with a 6809 CPU, Basic ROM, some RAM , VDU and PS/2 Kb. controller (sorry for the typo...):